臺大學術卓越系列報導 — 電資學院:利用超薄氧化層金氧半穿隧元件耦合機制之創新半導體元件應用

在現今積體電路元件密度高間距小的挑戰下,元件間之電性互相影響相當重要,研究如何應用特殊製程及元件架構,使得元件間的耦合現象得以控制並加以應用,為本報導的主要訴求。電資學院電機系與電子所合聘教授胡振國研究團隊研究矽基超薄氧化層技術多年,在超薄氧化層金氧半穿隧二極體(MIS TD)耦合效應機制與元件應用探索,發現有多項特徵為前所未見,重要指標已達世界紀錄,因元件結構與現今CMOS製程相容,具前瞻性與應用性,以多項專利申請與論文發表展現半導體元件創新研究能量。

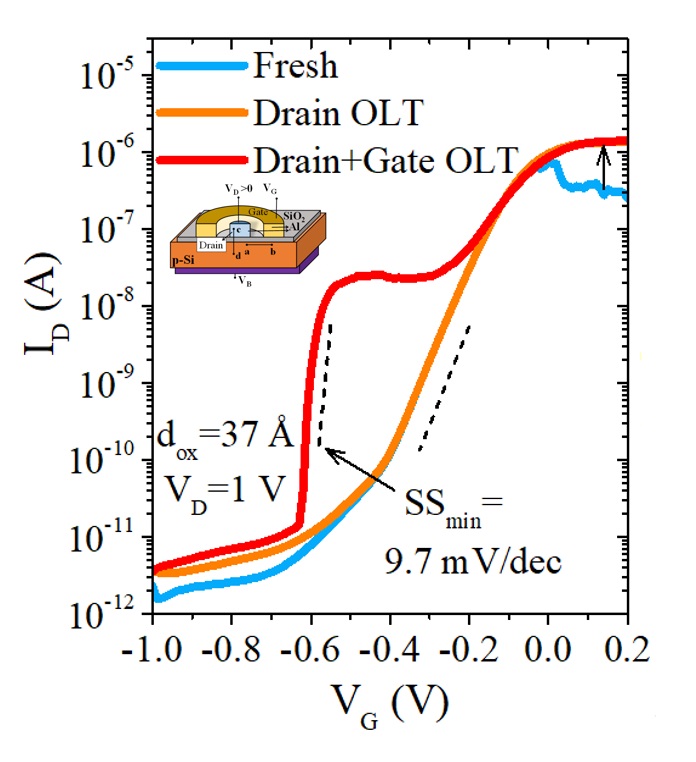

研究發現利用外環圍繞內圓電極架構之雙MIS TD架構,將中央MIS(p)固定偏壓VD,因氧化層穿隧機率大,造成少數載子缺乏,進而使電流趨飽和,外環MIS(p)給予負VG,少數載子能量提升但數量減少,經耦合使中央MIS(p)電流減少呈現電晶體特徵。給予PVS (positive voltage stress),氧化層達局部薄化,元件電流呈現提早飽和,稱為OLT (oxide local thinning),使得中央MIS(p)可工作於小偏壓而電流提升。經Drain OLT後,ON電流提升,再經Gate OLT,可使SSmin有效減少至小9.7 mV/dec,為矽基元件紀錄。

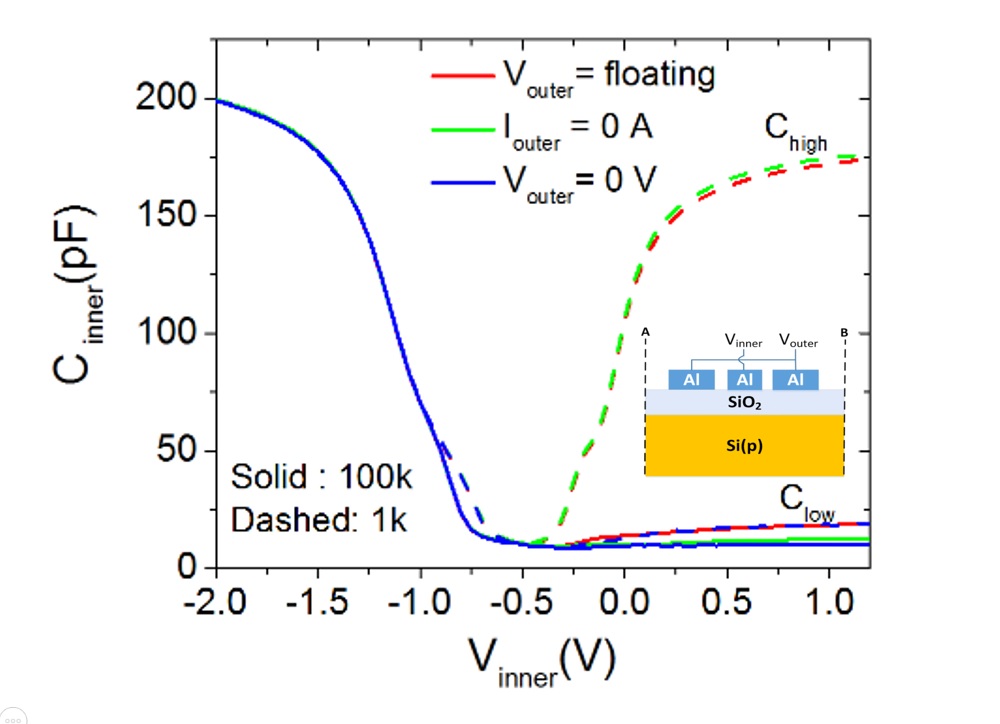

另一發現為中央MIS(p)電容值於反轉區受外環MIS(p)閘極之電位影響甚鉅,於閘極開路時 (Iouter = 0 A)反轉電容值大,於閘極短路時 (Vouter = 0 V),電容值降低,因中央MIS(p)於反轉區之偏壓固定,故少數載子數量固定,電容值差異明顯受外環Vouter影響,為前所未見。因閘電極操作於0 A與0 V時均屬無額外功率消耗,電路整合容易,電容雙態可做記憶體應用。給予Iouter = 0 A得到Chigh,切換至Vouter = 0 V得到Clow,可重複多次操作雙態電容穩定。

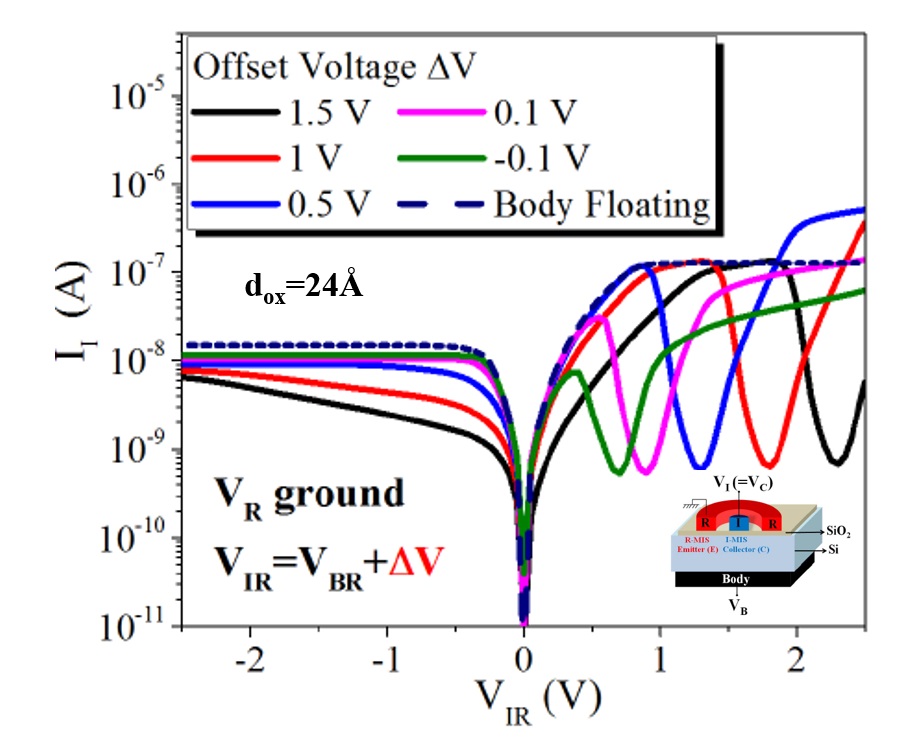

此外,若將元件耦合結構中基板偏壓給予適當改變,內外電極間之耦合條件會隨之改變,使得負轉導特徵為可調整,為前所未見。研究發現經由適當的offset voltage △V (= VIB)選取,當內外電極間電壓VIR變化時,負轉導會受△V影響,可呈現不同之負轉導出現區,相當靈敏。因為工作區可調整,對電路整合有很大的設計空間,具有前瞻元件之功效。所得到之最大 Peak to Valley Current Ratio (PVCR)達103以上,為矽基元件紀錄。

整體研究發現,當元件彼此間距離持續縮短時,元件間的耦合現象與互相影響相當明顯,相對的電場分布與元件應用研究將更具挑戰,本團隊提出的創新研究成果,結合超薄氧化層製程,清楚呈現耦合現象,這是個值得繼續深入研究的奈米元件議題。